EDA Solution

NanDigits

| EDA Solution

회사 소개

NanDigits Design Automation은 2007년에 설립된 캘리포니아 산호세에 위치한 EDA 회사입니다. 당사의 전문 기술은 기능적 Netlist ECO(Engineering Change Order), 기능적 안전 오류 검증(Verification) 및 넷리스트 디버깅(Netlist Debug) 서비스를 제공하는 데 있습니다. 당사의 GOF 플랫폼은 GOF ECO, GOF Formal, GOF LEC 및 GOF 디버깅의 네 가지 기능적 구성 요소로 구성되어 있습니다.

당사는 시장에서 최고의 기능성 Netlist ECO 툴인 GOF ECO를 제공하는 것을 목표로 하며, GOF ECO는 경쟁사에 비해 가장 작은 패치 크기의 기능성 Netlist ECO를 달성하였습니다. 또한 자동차 IC 시장 진출을 위한 노력을 지속적으로 하고 있습니다.

NanDigits Design Automation은 2007년에 설립된 캘리포니아 산호세에 위치한 EDA 회사입니다. 당사의 전문 기술은 기능적 Netlist ECO(Engineering Change Order), 기능적 안전 오류 검증(Verification) 및 넷리스트 디버깅(Netlist Debug) 서비스를 제공하는 데 있습니다. 당사의 GOF 플랫폼은 GOF ECO, GOF Formal, GOF LEC 및 GOF 디버깅의 네 가지 기능적 구성 요소로 구성되어 있습니다.

당사는 시장에서 최고의 기능성 Netlist ECO 툴인 GOF ECO를 제공하는 것을 목표로 하며, GOF ECO는 경쟁사에 비해 가장 작은 패치 크기의 기능성 Netlist ECO를 달성하였습니다. 또한 자동차 IC 시장 진출을 위한 노력을 지속적으로 하고 있습니다.

제품 개요

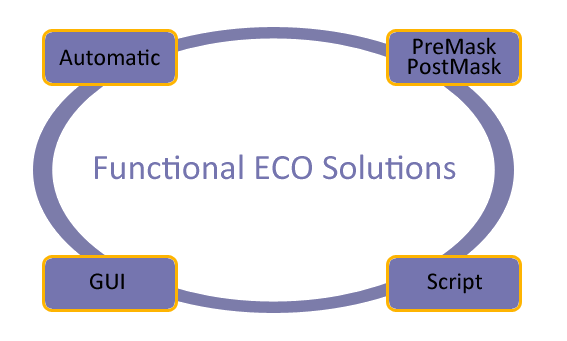

GOF ECO 는 GOF 플랫폼 내의 기능성 넷리스트(Netlist) ECO 툴로 첨단 기술과 방법론(Methodology)을 통합하여 종합적인 기능성 넷리스트(Netlist) ECO 솔루션을 제공합니다.

- 자동 기능 ECO는 넷리스트(Netlist)를 사용하여 구현 넷리스트를 수정합니다. 더보기

- RTL 유도 방식의 자동 기능 ECO 는 더 빠르고 더 정확한 ECO 결과를 생성합니다. 더보기

- RTL 패치 ECO는 전체적(full scale)이고 긴 합성 프로세스를 방지하여 처리 시간을 단축할 수 있습니다. 더보기

- 내장된 논리 동등성 검사 엔진으로 ECO 자체적으로 억제합니다. 더보기

- 병렬 처리를 통해 여러 CPU 코어를 최대한 활용하여 ECO 실행 시간을 단축합니다. 더보기

- Metal only ECO의 표준 스페어 셀은 마스크 후 ECO의 스페어 게이트만 재매핑(remap)합니다. 더보기

- GUI와 스크립트 모드가 혼합된 자동 모드 ECO는 ECO 패치를 최대한 최적화합니다. 더보기

- ECO 리타겟팅(Retargeting)은 단기간에 거대한 넷리스트 ECO를 달성합니다. 더보기

- DFT 친화적으로 테스트 로직(Test logic)을 그대로 유지하여 후기 설계 단계에서 두 번째 ECO 발생을 방지합니다. 더보기

- 자동 기능 ECO는 넷리스트(Netlist)를 사용하여 구현 넷리스트를 수정합니다. 더보기

- RTL 유도 방식의 자동 기능 ECO 는 더 빠르고 더 정확한 ECO 결과를 생성합니다. 더보기

- RTL 패치 ECO는 전체적(full scale)이고 긴 합성 프로세스를 방지하여 처리 시간을 단축할 수 있습니다. 더보기

- 내장된 논리 동등성 검사 엔진으로 ECO 자체적으로 억제합니다. 더보기

- 병렬 처리를 통해 여러 CPU 코어를 최대한 활용하여 ECO 실행 시간을 단축합니다. 더보기

- Metal only ECO의 표준 스페어 셀은 마스크 후 ECO의 스페어 게이트만 재매핑(remap)합니다. 더보기

- GUI와 스크립트 모드가 혼합된 자동 모드 ECO는 ECO 패치를 최대한 최적화합니다. 더보기

- ECO 리타겟팅(Retargeting)은 단기간에 거대한 넷리스트 ECO를 달성합니다. 더보기

- DFT 친화적으로 테스트 로직(Test logic)을 그대로 유지하여 후기 설계 단계에서 두 번째 ECO 발생을 방지합니다. 더보기

그림1. ECO Solutions

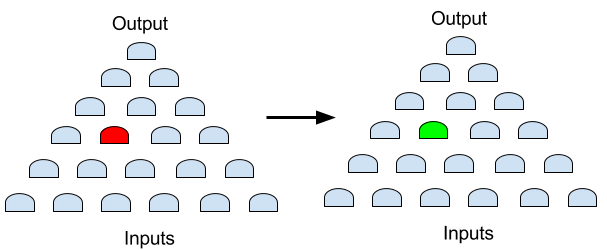

이 도구는 글로벌 모드와 증분 모드 모두에서 자동 ECO를 수행합니다. 글로벌 모드는 디자인의 전체 그림을 가질 수 있으며 ECO 결과는 동등함을 보장할 수 있습니다.

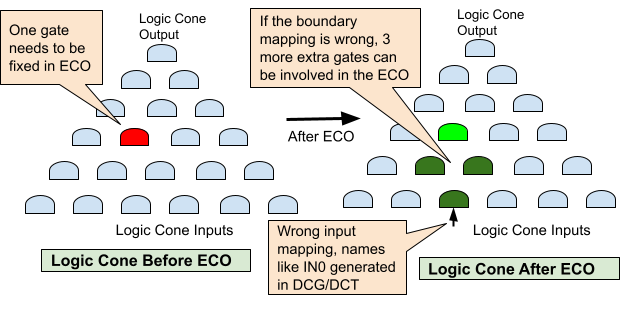

시놉시스(Synopsis) 디자인 컴파일러 지형학(DCT)과 디자인 컴파일러 그래픽(DCG)은 평면 계획, 라우팅 및 타이밍을 위해 넷리스트(Netlist)를 최적화하는 도구입니다. 그러나 이러한 도구들은 기능적인 ECO를 더 어렵게 만들 수 있습니다. 합성하는 동안 그들은 계층적 모듈 경계를 변경하여 클론 포트(clone ports)를 추가하거나 원래 포트의 상(Phase)을 반전(Invert)시키고 플롭(Flop)을 병합(Merge)할 수 있습니다.

Conformal ECO는 기능적인 ECO에서 포트 매핑(Mapping)에 문제가 있습니다. 그림 2와 같이 Conformal ECO는 DCG/DCT에서 추가한 클론 포트를 잘못 매핑하여 로직(Logic)을 수정하는 데 필요한 것보다 3배 더 많은 게이트(Gate)가 사용됩니다.

그림3. Boundary mapping affects ECO quality

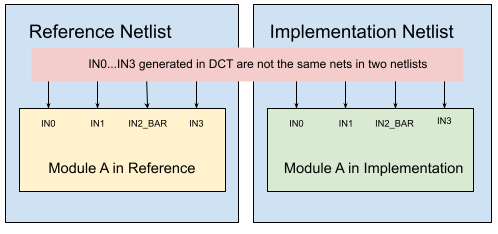

합성 툴(Synthesis tool)은 참조(Reference) 넷 리스트와 구현(Implementation) 넷 리스트 사이에 일대일 매핑(Mapping)이 없는 복제 포트를 추가합니다. ECO 도구가 이러한 포트를 동일하게 만들려고 하면 ECO 패치에 중복 게이트가 추가되거나 최종 로직(Logic)이 동일하지 않게 만들 수 있습니다.

그림4. DCG/DCT Boundary optimized netlist

그러나 GOF는 클론 포트를 올바르게 매핑(Mapping)하여 정확한 비동등점(Non-Equivalent point)만 고정할 수 있습니다.

그림5. GOF result, only the red spot is fixed