EDA Solution

Precision

| Siemens

Precision FPGA Synthesis

Precision은 공급 업체에 독립적인 FPGA 합성을 제공합니다. 동급 최고의 성능과 면적, 높은 신뢰성 설계 기능을 제공하며 시뮬레이션 및 공식 동등성 검사에 대한 긴밀한 연결을 제공합니다.

Precision FPGA Synthesis

Precision은 공급 업체에 독립적인 FPGA 합성을 제공합니다. 동급 최고의 성능과 면적, 높은 신뢰성 설계 기능을 제공하며 시뮬레이션 및 공식 동등성 검사에 대한 긴밀한 연결을 제공합니다.

KEY FEATURES

Industry-leading FPGA synthesis

Precision은 HDL(VHDL, Verilog, SystemVerilog) code 와 Synopsys Design Constraint(SDC)를 이용하여, 원하는 성능의 FPGA Netlist로 변환 해 주는 FPGA Synthesis 툴 입니다.

모든 FPGA를 지원함으로써 Design Architecture에 따라 최적의 FPGA Device를 선정하여 사용할 수 있습니다.

KEY FEATURES

Industry-leading FPGA synthesis

Precision은 HDL(VHDL, Verilog, SystemVerilog) code 와 Synopsys Design Constraint(SDC)를 이용하여, 원하는 성능의 FPGA Netlist로 변환 해 주는 FPGA Synthesis 툴 입니다.

모든 FPGA를 지원함으로써 Design Architecture에 따라 최적의 FPGA Device를 선정하여 사용할 수 있습니다.

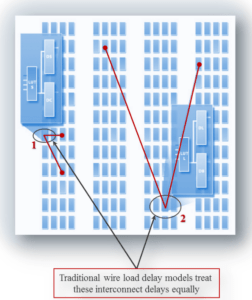

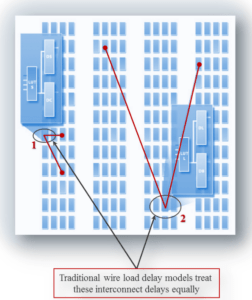

기존의 합성기법은 FPGA vendor에서 제공하는 cell과 wire load delay model base의 interconnect delay를 이용하여 Critical path를 계산하기 때문에 FPGA 내의 interconnect delay 정보가 모두 같게 계산됩니다. 요즘 FPGA의 성능은 interconnect의 path delay에 따라 성능이 좌우 되고 있으며 미세공정의 FPGA에서 interconnect delay가 증가하고 있습니다.

위 그림의 두 Path에 대한 Delay가 기존의 FPGA Synthesis 툴에서는 interconnect delay를 동일하게 취급하는 문제가 있으며 이러한 문제를 해결하기 위해 Mentor에서는 Physically Aware Optimization을 이용한 합성 기능을 제공하고 있습니다.

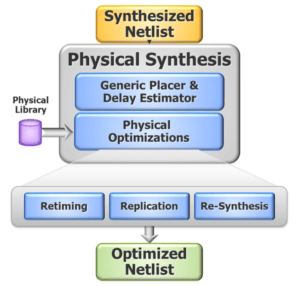

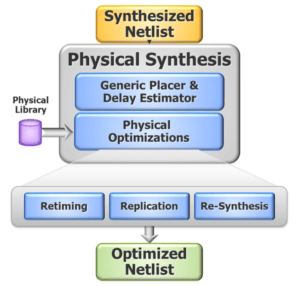

Physically Aware Optimization은 위 그림과 같이, 기존의 합성 결과의 Critical path에 대해 Generic Place와 Delay Estimator를 이용하여 Logic의 위치정보 및 Routing Resources를 고려함과 동시에, Retiming, Replication, Re-Synthesis 기법을 활용하여 최적의 Netlist를 도출할 수 있게 도와 줍니다. 또한 최적화된 Netlist를 사용하게 되면 많은 시간이 소요되는 P&R 시간을 단축할 수 있습니다.

주요 특징

기존의 합성기법은 FPGA vendor에서 제공하는 cell과 wire load delay model base의 interconnect delay를 이용하여 Critical path를 계산하기 때문에 FPGA 내의 interconnect delay 정보가 모두 같게 계산됩니다. 요즘 FPGA의 성능은 interconnect의 path delay에 따라 성능이 좌우 되고 있으며 미세공정의 FPGA에서 interconnect delay가 증가하고 있습니다.

위 그림의 두 Path에 대한 Delay가 기존의 FPGA Synthesis 툴에서는 interconnect delay를 동일하게 취급하는 문제가 있으며 이러한 문제를 해결하기 위해 Mentor에서는 Physically Aware Optimization을 이용한 합성 기능을 제공하고 있습니다.

Physically Aware Optimization은 위 그림과 같이, 기존의 합성 결과의 Critical path에 대해 Generic Place와 Delay Estimator를 이용하여 Logic의 위치정보 및 Routing Resources를 고려함과 동시에, Retiming, Replication, Re-Synthesis 기법을 활용하여 최적의 Netlist를 도출할 수 있게 도와 줍니다. 또한 최적화된 Netlist를 사용하게 되면 많은 시간이 소요되는 P&R 시간을 단축할 수 있습니다.