EDA Solution

Custom IC Design (Tanner)

| Siemens

Tanner

Tanner Digital Implementer

태너 디자이너(Tanner Designer)는 프로젝트에 대한 모든 시뮬레이션을 추적하는 아날로그 검증 관리 도구입니다. 이 도구는 시뮬레이션 결과를 편리한 대시보드에 표시하여 팀이 어떤 블록이 사양에 합격 또는 불합격되는지 빠르게 확인하고 검증 진행 상황을 모니터링할 수 있도록 합니다.

Custom IC Design (Tanner)

Analog/Mixed-Signal 시뮬레이션 및 검증 관리

KEY FEATURES

Take control of verification management

Custom IC Design(Tanner) 솔루션은 Analog/Mixed-Signal(AMS) IC Design 을 위한 완전하고 고도로 통합된 End-to-End Flow 를 제공하며, 최소한의 비용으로 완벽한 AMS 설계를 구현할 수 있도록 지원합니다.

- S-EDIT Schematic Capture

- L-EDIT IC Layout

- T-SPICE Simulation

- Custom IC Waveform Viewer

- Tanner Calibre One Verification Suite

복잡한 Analog/Mixed-Signal IC Design 설계를 위한 사용자 친화적인 Schematic Capture

S-EDIT 는 아날로그 혼합 신호(AMS) IC 설계를 위한 종합적인 설계 캡쳐 환경으로,

가장 복잡한 혼합 신호 IC 설계를 처리하면서 생산성을 향상시키고 회로도 생성, 시뮬레이션 설정, 실행 및 결과 분석을 지원합니다.

– 엄격한 SPICE 시뮬레이션 통합 및 Waveform cross-probing 을 포함한 업계 표준 지원

– Schematic 에서 원하는 지점의 시뮬레이션 결과를 확인 가능

– Schematic and Layout, Layout and LVS 보고서 간의 cross-probing.

– Schematic 에 대한 Electrical Rule Checks (ERC)

– Advance array 와 Bus 지원

– L-Edit IC 와 통합되어 Layout 및 ECO 프로세스 속도 향상

– Windows 및 Linux 에서 사용 가능

– OA Support

– Easy to Use

직관적이며, 쉬운 Learing Curve 로 빠르게 S-EDIT 사용 가능

– Multiple views per Cell

Cell 에 대해 SPICE, schematic, Verilog, Verilog-A 그리고 Verilog-AMS 까지 다양한 형태의 View 를 제공

– Industry-standard import and export support

SPICE, EDIT, Verilog, VHDL 출력 지원 / OpenAccess, EDIT 및 3rd Party Tool 의 데이터 불러오기 가능

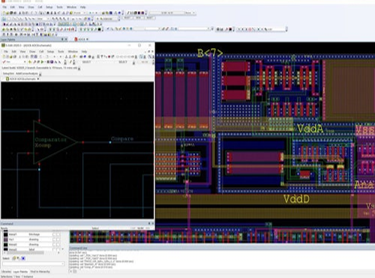

복잡한 Analog/Mixed-Signal IC Design 설계를 위한 사용자 친화적인 Physical Layout

아날로그 혼합 신호(AMS) 설계를 위한 고용량 계층적 IC 레이아웃 편집기로

표준(OpenAccess, iPDK, TCL)을 기반으로 구축되었으며, 복잡한 레이아웃을 효율적으로 구현하고 물리적 검증을 수행하는 데 필수적인 기능을 제공합니다.

– OA Support

– Real-Time Net Flylines

– Nets & Pins Tracking

– ECO Tracking

– Geometry Marking/Highlighting By Net

– Windows 및 Linux 에서 사용 가능

– Complete Hierarchical Physical Layout

Object-snapping, Node highlighting, Layout generators 와 Macro 지원을 포함한 다양한 편의 기능 제공

– Supports Critical Industry Standards

OpenAccess 의 읽기/쓰기 와 Schematic Driven Layout (SDL) 지원

T-SPICE, HSPICE, PSpice, Structural Verilog 와 CDL formats 의 Netlist 지원

– Optimized Performance

빠른 렌더링 속도와 대화형 Real-Time Design Rule Checking (DRC) 기능

– L-EDIT Photonics

– Direct Calibre/Calibre RVE Support with EVI

Tanner EVI ( External Verification Interface ) 를 이용하여 L-EDIT 내에서 Calibre Tool Set 통합 사용 가능

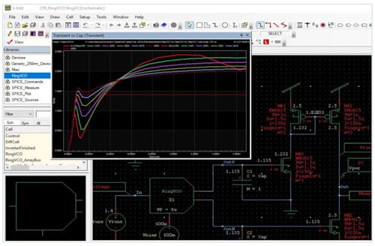

Analog/Mixed-Signal Design 을 위한 빠르고 정확한 Foundry-Proven Simulation

T-SPICE Simulator 는 Custom IC Design Flow 상의 다른 제품들과 쉽게 통합 연동을 지원하는 업계 표준을 지원하는 Simulator 입니다. Advanced Modeling, Device-State Plotting 그리고 Real-Time Waveform Viewing and Analysis 를 지원하여 정확한 Simulation 결과를 보거나 분석할 수 있습니다.

– 가상 데이터 측정, 파라미터 스위핑, Monte Carlo 분석을 이용하여 회로 동작을 정확하게 특성화

– Windows 및 Linux 에서 사용 가능

– Intuitive and Easy to Use

– Foundry-Proven

RTL go GDSII, PDKs 지원

– Supports Key Industry Standards

모든 DEVICE 의 맞춤형 고급 모델링을 위한 Verilog-A, Verilog-AMS 모델 생성 지원

Tanner Waveform Viewer (이전 W-EDIT) 제품은 직관적인 Multiple-Window 와 Multiple-Chart 를 통해 시뮬레이션 결과 파형을 쉽게 분석 및 비교할 수 있으며, 시뮬레이터인 T-SPICE 와 Schematic Capture 인 S-EDIT 이 연동되어 S-EDIT 으로부터 쉽게 데이터를 불러올 수 있습니다.

– Schematic Capture 인 S-EDIT 과 Waveform Data Direct Cross Proving 을 지원합니다.

– Advanced Analysis 를 위해 새로운 trace 생성 및 측정 데이터의 max, min, average, intersect, rms, over/undershoot, amplitude, error, crossing, delay, period, frequency, rise/falltime, jitter, pulse width, settling time, integral, derivative, duty cycle, 그리고 slew rate 까지 확인을 할 수 있습니다.

– Automactically Calculate & Display FFT Results

dB or Linear magnotude

Wrappeed or unwrapped phase

Use for real or imaginary parts

– Multiple Simulations

Tanner Waveform Viewer 는 동시에 여러 시뮬레이션 결과 보기를 지원하므로 다양한 조건의 시뮬레이션 결과를 비교 및 측정하기 유용하며, 시뮬레이션 하나 이상의 결과 파일에서 다른 조건의 시뮬레이션 결과를 로드하고 Chart창에 복사 할 수 있습니다. AMS 를 진행하시는 경우에는 VCD 파일을 로드하여 디지털 결과도 같이 확인 가능

– Programmable

Tanner Waveform Viewer 는 잘 알려져 있는 TCL 를 이용하고 GUI 상으로 할 수 있는 다양한 작업을 진행하는 스크립트를 작성하여 사용 가능

– Chartbooks

Tanner Waveform Viewer 는 Chart 에 기록되는 모든 정보를 저장하는 chartbook 를 생성하며, 후속 시뮬레이션 결과와 비교를 하기 위해 Chartbook 에 저장된 Data 를 불러오고, 해당 파형을 복사 및 측정을 하는 것이 가능

업계 표준 제품인 Calibre® DRC, LVS 및 xRC 를 사용하여 Analog/Mixed-Signal IC Design 의 Tape-out-sign-off 검증을 수행할 수 있습니다.

Tanner-Caliber One IC 검증 제품군은 Tanner ™ Analog/Mixed-Signal (AMS) 물리적 설계 환경의 핵심적인 부분으로, 검증된 Calibre Verification Tool 에 대한 쉬운 사용 경로를 제공합니다.

– Schematic Capture 와 Physical Layout 제품인 S-EDIT 와 L-EDIT 상에서 Calibre® DRC, LVS 및 xRC 를 사용 할 수 있도록 EVI 를 통해 긴밀하게 통합되어 있습니다.

– Caliber 플랫폼은 Physical Verification 을 위한 업계 선도 제품이며 모든 주요 IC 파운드리의 Sign Off 자격이 있으며 Tanner Caliber® One Verification Suite 역시 동일한 Calibre 디자인 키트를 사용합니다.

– Calibre nmDRC (Hierarchical Design Rule Checking)

빠른 사이클 타임과 혁신적인 Design Rule Check 기능을 제공

– Calibre xRC (Parasitic Extraction)

레이아웃 종속 효과가 설계의 전기적 성능에 악영향을 미치지 않고 포괄적이고 정확한 레이아웃 후 분석 및 시뮬레이션을 위한 정확한 기생 데이터를 제공하는지 확인

– Calibre nmLVS (Hierarchical Layout Versus Schematic)

Physical Layout 이 Schematic 과 전기적, 지형학적으로 동일한지 확인하며, 실제 Device Geometry 측정 및 대화형 디버깅 기능을 제공하여 정확한 검증을 보장함으로써 디자이너 생산성을 향상

– Calibre RVE (Graphical Results Viewing Environment)

디자인 문제를 시각적으로 식별하고 S-EDIT 및 L-EDIT 에서 관련 문제를 교차 선택함으로써 디버깅 시간을 단축할 수 있는 환경을 제공